VIA C3 vs VIA C7 zegar w zegar

Dawno, dawno temu, zanim komukolwiek śniły się Ryzeny R3 i R7, a intelowskie I3 i I7 były co najwyżej w odległych planach istniały inne, podobnie nazwane procesory. VIA C3 i C7. Mało kto je pamięta, a Ci którzy pamiętają uśmiechają się pewnie z politowaniem. Niekoniecznie słusznie.

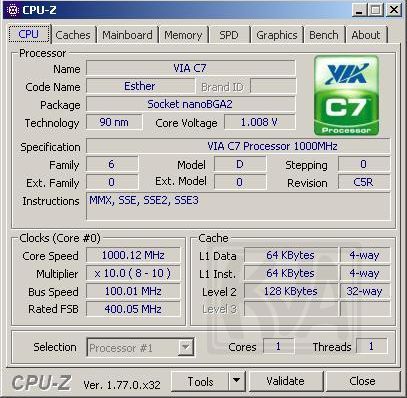

Skąd taka nazwa? C3 to skrót od Cyrix III. VIA po wykupienia producentów Cyriksa porzuciła źle kojarzącą się markę. Pierwsze wersje rdzenia, znane jako Samuel 2 i Ezra/Ezra-T były naprawdę słabe. Ich główną wadę stanowiło FPU taktowane jedynie z połową predkości procesora. Ogromnym skokiem był rdzeń Nehemiah gdzie problem ten rozwiązano, przy okazji wprowadzając wiele innych usprawnień. Choć nadal oficjalnie był to procesor C3 to nazywano go czasem C5 dla podkreślenia różnic. Ostatecznie VIA zdała sobie chyba sprawę z zamieszania z kolejnymi, znacznie różniącymi się wydajnością procesorami o identycznej nazwie i wydała VIA C7 znany jako Esther.

Historia procesorów VIA jest bardzo ciekawa i zasługuje na osobny, szczegółowy artykuł, który niewątpliwie za jakiś czas opublikuję. Tutaj ograniczę się do sprawdzenia jak duże zmiany w IPC nastąpiły pomiędzy VIA C3 Nehemiah, a VIA C7 Esther.

| VIA C3 Nehemiah | VIA C7 Esther | |

| Taktowanie: | 1000MHz | 1000MHz |

| L1 cache: | 128KB | 128KB |

| L2 cache: | 64KB | 128KB |

| TDP: | 15W | 9W |

| Litografia: | 130nm | 90nm |

| Zestawy instrukcji: | MMX, SSE | MMX, SSE, SSE2, SSE3 |

| Data wprowadzenia: | Styczeń 2003 | Maj 2005 |

Oba procesory projektowane były z tym samym, podstawowym założeniem - im niższy pobór prądu tym lepiej. Wynikało to z faktu, że wydajność procesorów Intela i AMD w tym okresie była zupełnie poza zasiegiem małego zespołu inżynierów VIA. Zamiast jednak zrezygnować z produkcji procesorów x86, firma znalazła swoją niszę w postaci systemów wbudowanych, mini komputerów, kiosków multimedialnych czy bankomatów. Tam wydajność, o ile była wystarczająca, nie musiała być duża. Ważna była cena i właśnie pobór prądu.

W celu jego minimalizacji należało zrezygnować z wielu ważnych, ale prądożernych elementów CPU, w taki sposób by spadek wydajności był jak najmniejszy.

Inżynierowie stwierdzili, że możliwość wykonywania instrukcji poza kolejnością (out-of-order execution) co prawda podnosi znacząco wydajność w niektórych zastosowaniach, ale jest bardzo kosztowna zarówno energetycznie jak i sprzętowo. Do tych samych wniosków doszli kilka lat później pracownicy Intela projektując pierwszego Atoma!

Spadek wydajności częściowo starano się skompensować relatywnie dużym cache L1 (128KB w obu testowanych dziś CPU) i dobrze działającym mechanizmem przewidywania skoków.

W efekcie powstały rzeczywiście bardzo oszczędne CPU, mogące w wolniejszych wersjach pracować bez aktywnego chłodzenia. Wydajność wystarczała do zastosowań przemysłowych, w domowych była jednak tragiczna. Pentium III 1000MHz Coppermine był kilkukrotnie wydajniejszy od VIA C3 1000MHz choć pojawił się trzy lata wcześniej. Z drugiej jednak strony miał trzykrotnie wyższe TDP i znacznie wyższą cenę.

Wraz z wprowadzeniem rdzenia Esther próbowano temu zaradzić - poprawiano mechanizm przewidywania skoków, zwiększono cache L2, dodano SSE2 i SSE3. Dzięki wprowadzeniu nowego procesu produkcji (90nm w miejsce 130nm) zmiany te nie odbiły się na poborze prądu. Wręcz przeciwnie, identycznie taktowany C7 miał niższy pobór od starszego C3.

Pora omówić platformy na których pracowały testowane CPU.

>> Platformy testoweSpis treści:

VIA C3 vs VIA C7 zegar w zegarPlatformy testowe

Testy syntetyczne - matematyka

Testy syntetyczne - rendering

Testy syntetyczne - wydajność pamięci

Testy syntetyczne - szachy, kompresja i szyfrowanie

Testy rzeczywiste - Irfanview 4.30

Testy rzeczywiste - kompresja, szyfrowanie, wyszukiwanie

Testy rzeczywiste - BOINC

Testy pod Linuksem

3DMark 2001

3DMark 2003 i AquaMark3

Pobór prądu i podsumowanie